# **ELE 375 / COS471B, COS 471A Midterm Fall 2003**

**Prof:**

**David August**

TAs:

Neil Vachharajani

**David Penry**

For grading

| Question | Score                  | 1                        |

|----------|------------------------|--------------------------|

| I        | 20 /20                 | $\mathcal{A}\mathcal{C}$ |

| II       | 20 <b>/20</b>          | NV                       |

| III      | 20 /20                 | DA                       |

| IV       | 20 /20                 | DP                       |

| TOTAL    | <i>8</i> 0 / <b>80</b> |                          |

Please write your answers clearly in the space provided. For partial credit, show all work. State all assumptions. You have 1 hour and 20 minutes for this exam. This midterm is closed book. Only one two-sided, handwritten 8.5x11 sheet is allowed. Put your name on every page. Write out and sign the Honor Code pledge before turning in the test. "I pledge my honor that I have not violated the Honor Code during this examination."

| NAME: _  | Sol           | Ution          |         |

|----------|---------------|----------------|---------|

| COURSE ( | (circle one): | COS471B/ELE375 | COS471A |

| HONOR C  | ODE:          |                |         |

### **QUESTION I:**

Answer the following questions. Circle your final answer. Consider the following assembly code for parts 1 and 2. (Assume no branch delay slot in this architecture.)

1. During the execution of the above code, how many dynamic instructions are executed?

2. Assuming a standard unicycle machine running at 100KHz, how long will the above code take to complete?

200 inst x

$$\frac{1 \text{ cycle}}{\text{inst}} \times \frac{1 \text{ Sec}}{100,000 \text{ cycles}} = \frac{1}{500} \text{ Sec} = 2 \text{ ms}$$

3. Using our 8-bit IEEE 754 wimpy precision floating point with three (3) exponent bits and four (4) mantissa bits, show the representation of -11/16 (-0.6875).

$$B_{ias} = 2^{n-1} - 1 = 2^{2} - 1 = 3$$

$$\frac{+11}{16} = \frac{8}{16} + \frac{2}{16} + \frac{1}{16} = \frac{1}{2} + \frac{1}{8} + \frac{1}{16} \Rightarrow 0.1011_{2}$$

$$\frac{10100110}{\text{Sign}} \leftarrow \frac{1}{\text{Exp}} = \frac{1}{1011} = \frac{1}$$

4. What is the smallest positive (not including +0) representable number in our 8-bit IEEE 754 wimpy precision floating point? Show the bit encoding and the value in base 10 (fraction or decimal OK).

Smallest Denorm. Positive Denorm Smallest mant.

Bias = 3 Denorm exp is same as

$$001 = 7 l_{10}$$

$Exp = 1 - 3 = -2_{10}$  implied 0 in denorms

$0.0001 \times 2^{-2} = 72^{-6} = \boxed{\frac{1}{64}}$

5. Consider a unicycle machine implementation in which 40% of every cycle is spent performing instruction memory fetch. You invent and implement a technique which cuts fetch time in half. **Quantitatively**, what effect did this optimization have on latency and throughput?

Latercy is 0.80

$$\left(1 - \frac{40\%}{2}\right)$$

or  $\left[\frac{20\%}{50\%}\right]$  shorter.

Throughput is  $\frac{1}{1 - 0.4 + \frac{0.4}{2}} = \frac{1}{0.8} = \frac{5}{4} = \left[1.25 \times \text{more}\right]$

$$Speedup = \frac{1}{1 - f + \frac{f}{5}}$$

6. In the same machine, what is the maximum speedup possible by optimizing only instruction memory fetch?

Speedup =

$$\frac{1}{1-0.4+\frac{0.4}{\infty}} = \frac{5}{0.6} = \frac{5}{3} = 1.67$$

# **QUESTION II:**

Convert the C function on the next page to MIPS assembly language. Make sure that your assembly language code could be called from a standard C program (that is to say, make sure you follow the MIPS calling conventions).

This machine has no delay slots. The stack grows downward (toward lower memory addresses). The following registers are used in the calling convention:

| Register Name | Register Number | Usage                    |

|---------------|-----------------|--------------------------|

| \$zero        | 0               | Constant 0               |

| \$at          | 1               | Reserved for assembler   |

| \$v0, \$v1    | 2, 3            | Function return values   |

| \$a0 - \$a3   | 4 – 7           | Function argument values |

| \$t0 - \$t7   | 8 – 15          | Temporary (caller saved) |

| \$s0 - \$s7   | 16 - 23         | Temporary (callee saved) |

| \$t8, \$t9    | 24, 25          | Temporary (caller saved) |

| \$k0, \$k1    | 26, 27          | Reserved for OS Kernel   |

| \$gp          | 28              | Pointer to Global Area   |

| \$sp          | 29              | Stack Pointer            |

| \$fp          | 30              | Frame Pointer            |

| \$ra          | 31              | Return Address           |

```

This is the function you should convert:

```

```

unsigned int sum(unsigned int n)

{

if (n == 0) return 0;

else return n + sum(n-1);

}

```

```

SUM: add $ vo, $Zero, $Zero

; Initialize return value

beg $a0, $zero, return; If n == 0 goto return

addiu $ sp, $sp, -8

Make room on stack

; save n

$90, O($5P)

SW

$ ra, 4 ($ sp)

SW

Save return address

$00, $00, -1

addio

, n=n-1

jal

: $ VO = sum(n-1)

SUM

: restore n

lw $90, 0 ($sp)

1w $1a, 4 ($sp)

; restore return addr.

addis $ sp, $ sp, 8

; Discard stack frame

add $ vo, $ vo, $ a0

return value =

n+ sum (1-1)

return: jr sra

Return

```

## **QUESTION III:**

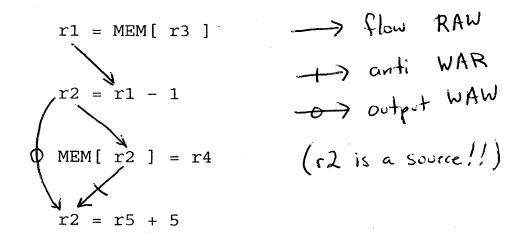

1. Draw the register dependence arcs that exist in the following code segment. Be sure to properly label each arc.

2. The architecture respects all dependences. The implementation of the machine you are targeting has a 3-cycle LOAD-USE data hazard. No other hazards exist.) The code segment above is a small part of a much larger program which you cannot change. Registers r1-r9 are used after this code segment. Registers r10-r20 are not used in this program at all. Write a more efficient version of the code segment (leave room in your answer for part 3). The resulting program which includes your new code segment must have equivalent functionality.

r = m Em [r3]

r = r5 + 5

r = r - 1

m Em [r12] = r 4

rename this r2 since other

r2 may be used in other

parts of the program.

3. Draw all the register dependence arcs that exist in your optimized code segment above.

(This r2 is not available to the rest of the program because r2=r5+5 overwrites it.)

### **QUESTION IV:**

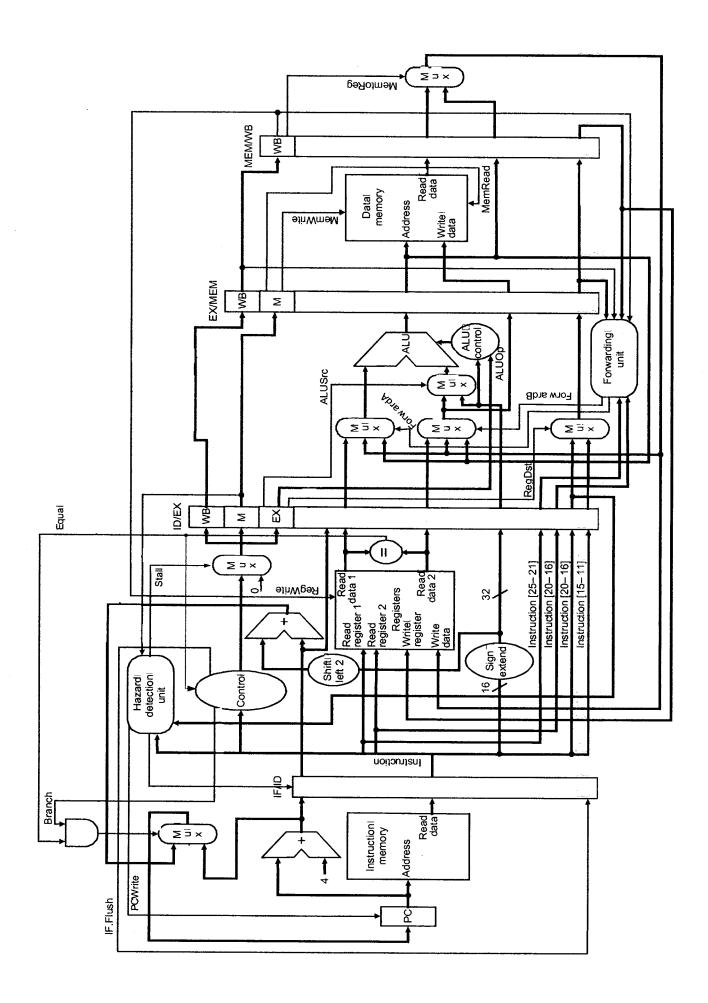

Consider the datapath on the last page. This machine does not support code with branch delay slots. (It predicts not-taken with a 1-cycle penalty on taken branches.)

For each control signal listed in the table on the next page, determine its value at cycles 3 through 9, inclusive. Also, show the instruction occupying each stage of the pipeline in all cycles. (Assume the IF/ID write-enable line is set to the inverse of the Stall signal.)

The initial state of the machine is:

PC = 0

All pipeline registers contain 0s

All registers in the register file contain 0s.

The data memory contains 0s in all locations

The instruction memory contains:

00: addiu \$3, \$zero, 4

04: lw \$4, 100(\$3)

08: addu \$2, \$4, \$3

0C: beq \$4, \$zero, 0x14

10: addiu \$3, \$3, 1

14: addiu \$2, \$2, \$3

all other locations contain 0

Use data forwarding whenever possible. All mux inputs are numbered vertically from "top" to "bottom" starting at 0 as you look at the datapath in the proper landscape orientation. Also, the values for ALUOp are:

| Value | Desired ALU Action                |

|-------|-----------------------------------|

| 00    | Add                               |

| 01    | Subtract                          |

| 10    | Determine by decoding funct field |

#### **Instruction formats:**

| <b>,</b> - | 6 bits | 5 bits         | 5 bits | 5 bits              | 5 bits | 6 bits |  |  |  |  |  |

|------------|--------|----------------|--------|---------------------|--------|--------|--|--|--|--|--|

| R: [       | op     | rs             | rt     | rd                  | shamt  | funct  |  |  |  |  |  |

| I: [       | op     | rs             | rt     | address / immediate |        |        |  |  |  |  |  |

| J: [       | op     | target address |        |                     |        |        |  |  |  |  |  |

|          | Jime<br>Time | <b>P</b> CWrite | IP. Flush | Branch      | Stall    | ALUSic                  | ALUOp   | RegDst       | ForwardA | ForwardB    | MemRead      | MemWrite | MemtoReg     | RegWrite 3 |

|----------|--------------|-----------------|-----------|-------------|----------|-------------------------|---------|--------------|----------|-------------|--------------|----------|--------------|------------|

|          |              | I               | F         |             | ID_      | EX                      |         |              |          | M           |              | WB       |              |            |

|          | 0            | 00: a           | ıddiu     |             |          |                         |         |              |          |             |              |          |              |            |

|          |              | 1               | 0         | 0           | 0        | 0                       | 00      | 0            | 00       | 00          | 0            | 0        | 0            | 0          |

|          | 1            | 04: lw          |           | 00:         | addiu    |                         |         | -L           |          |             |              | 1        |              |            |

|          |              | 1               | 0         | 0           | 0        | 0                       | 00      | 0            | 00       | 00          | 0            | 0        | 0            | 0          |

|          | 2            | 08: addu        |           | 04:         | lw       | 00:                     | addiu   | <u> </u>     | <u> </u> | 1           |              |          |              |            |

|          |              | 1               | 0         | 0           | 0        | 1                       | 00      | 0            | 00       | 00          | 0            | 0        | 0            | 0          |

|          | 3            | 00:             | beg       | 08:         | addu     | 0                       | 4: Iw   |              | BYPA     | <del></del> | $\vdash$     | ddia     |              | <u> </u>   |

| R        |              | (0)             | 0         | 0           | (1)      | 1                       | 00      | 0            | (10)     | 00          | X            | 0        | X            | 0          |

| R<br>7:5 | 4            | OC:             | beq       | 08:         | 7dlu     | L                       | DAD-1   | ISE<br>(NOI) | STALL    | <u>-</u>    | 04           | <u> </u> | <del> </del> | addia      |

| ble      |              | 1               | 0         | 0           | 0        | X                       | X       | X            | Х        | X           |              | 0        | (            | 1          |

| 7        | 5            | 10: 4           | 28diu     | din oc: beq |          | O8:21)u BYPASS WB TO EX |         |              | —(nob)   |             | 04:100       |          |              |            |

|          | <b>→</b>     | 1               |           |             | 0        | 0                       | 10      | 1            | (01)     | 00          | ·X           | 0        | 0            | 1          |

| >;       | 6            | 14: 2           | ddu       | TAKEN       | BRANCH ; | ALTY                    | oc:     | beq          | 1        | <b>I</b>    |              | 2 John   |              | -(MOP)     |

|          | ***          | - (             | 0         | 0           | 0        | ኧ                       | ×       | X            | X        | Х           | Х            | 0        | Х            | 0          |

| .        | 7            | (8: 1           | 109       | 14 ° a      | ddu      |                         | - (no)  |              |          |             | ocibea 08: a |          | du           |            |

|          |              | ſ               | 0         | 0           | O        | X                       | X       | χ            | X        | X           | Х            | 0        | 1            | 1          |

|          | 8            | 16:             | no p      | 18: nop     |          |                         | 14:230u |              |          | - (NOP)     |              | ٥٢:      | beq          |            |

|          |              | 1               | 0         | 0           | O        | 0                       | 10      | ı            | 00       | 00          | Х            | O        | Х            | 0          |

|          | 9            | 20:             | nop       | 161         | пор      |                         | (8      | nop          |          |             | 14: addiu    |          | <b>~</b> (   | NCP)       |

|          |              |                 | 0         | 0           | 0        | X                       | X       | χ            | λ        | X           | χ            | 0        | Χ            | 0          |

STALL FOR

LOAD-USE?

JSSERT STALL

to insert bubble

after ID and

de 255ct

Predictation.

Predictation.

Predictation.

Not taken,

so Flush

esserted to

esse

00: addiu \$3, \$zero, 4

04: lw \$4, 100(\$3)

"X" means don't care

08: addu \$2, \$4, \$3

0C: beq \$4, \$zero, 0x14

10: addiu \$3, \$3, 1 14: add**/**u \$2, \$2, \$3